# IR3Y38M

# **CCD Signal Process & Digital Interface IC**

#### **DESCRIPTION**

The IR3Y38M is a bipolar single-chip signal processing IC for CCD area sensors which includes correlated double sampling circuit (CDS), clamp circuit, automatic gain control amplifier (AGC), reference voltage generator, black level detection circuit, 10-bit analog-to-digital converter (ADC), and serial interface for internal circuits.

#### **FEATURES**

- Low power consumption : 315 mW (TYP.)

- Wide AGC range: 12 to 43.5 dB

- High speed sample-and-hold circuits: pulse width 12 ns (MIN.)

- Built-in standby mode for power saving applications

- Built-in serial interface to control the AGC gain, maximum gain and offset adjustment

- 10-bit ADC operating up to 18 MHz

- Digital interface for operating 3.3 V logic ICs

- Single +5 V power supply

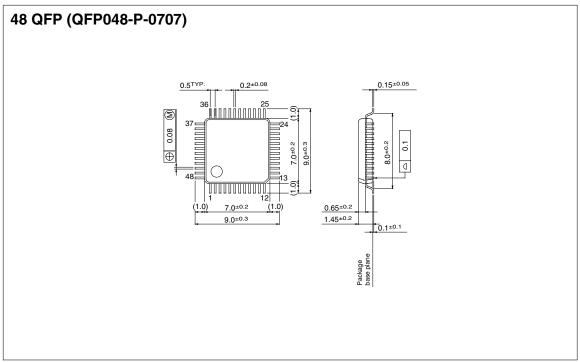

- Package : 48-pin QFP (QFP048-P-0707) 0.5 mm pin-pitch

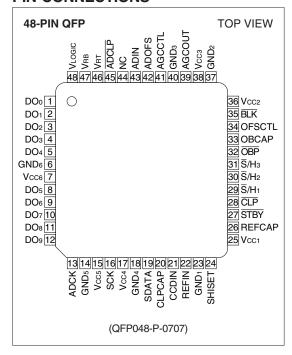

#### PIN CONNECTIONS

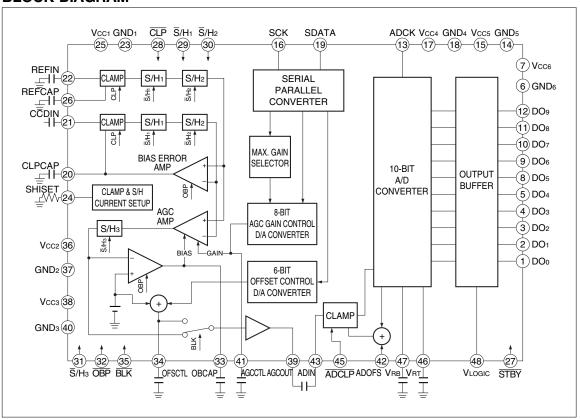

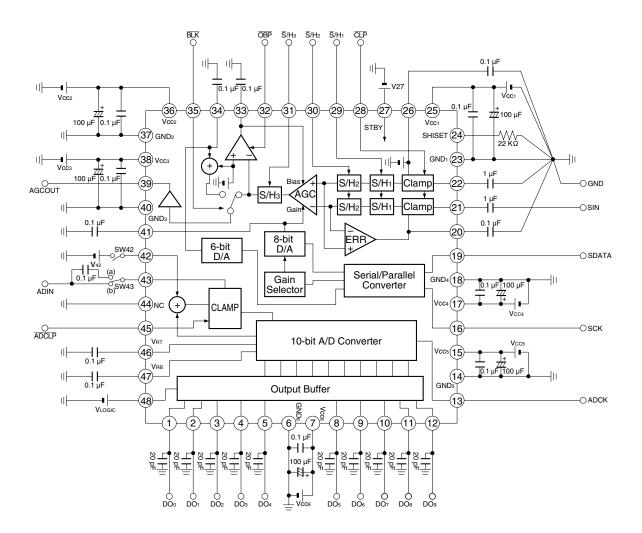

### **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

(The voltage is measured on condition that VCC1 to VCC6 = +5.0 V, VLOGIC = +3.3 V.)

| PIN NO. | PIN NAME        |         | EQUIVALENT CIRCUIT                    | DESCRIPTION                                                                                                                                                                                  |

|---------|-----------------|---------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DO <sub>0</sub> |         | Vccs                                  | Digital data output pins of the A/D                                                                                                                                                          |

|         |                 |         | 500 ≩ ▼                               | converter. DO <sub>0</sub> is LSB.                                                                                                                                                           |

| 2       | DO <sub>1</sub> | 3.1 V   | <del></del>                           | The data format is a straight binary                                                                                                                                                         |

| 3       | DO <sub>2</sub> |         | * 200<br>W                            | code.                                                                                                                                                                                        |

| 4       | DO <sub>3</sub> | 0.2 V   | · · · · · · · · · · · · · · · · · · · | Vol.: 0.2 V (TYP.)                                                                                                                                                                           |

| 5       | DO <sub>4</sub> |         | 10 k ₹ <b>T</b> GND6                  | Voh : VLogic – 0.2 V (TYP.)                                                                                                                                                                  |

| 6       | GND6            | 0.0 V   |                                       | GND pin of the output buffer of the A/D converter.                                                                                                                                           |

| 7       | VCC6            | 5.0 V   |                                       | Power supply pin of the output buffer of the A/D converter.                                                                                                                                  |

| 8       | DO <sub>5</sub> |         | Vcc6                                  | Digital data output pins of the A/D                                                                                                                                                          |

| 9       | DO <sub>6</sub> | 3.1 V   | 500 \$                                | converter. DO9 is MSB.  The data format is a straight binary                                                                                                                                 |

| 10      | DO <sub>7</sub> |         | 200                                   | code.                                                                                                                                                                                        |

| 11      | DO8             | 0.2 V   | <b>→ →</b>                            | Vol.: 0.2 V (TYP.)                                                                                                                                                                           |

| 12      | DO <sub>9</sub> |         | GND <sub>6</sub>                      | VOH : VLOGIC - 0.2 V (TYP.)                                                                                                                                                                  |

| 13      | ADCK            | > 2.1 V | 150 µ (GNDs)                          | Clock input pin of the A/D converter.  The A/D conversion is executed at the rising edge of the ADCK, and the data is output at the falling edge of the ADCK.  Duty: 50% fmax: 18 MHz (MIN.) |

| 14      | GND5            | 0.0 V   |                                       | Digital GND pin of the A/D converter.                                                                                                                                                        |

| 15      | VCC5            | 5.0 V   |                                       | Digital power supply pin of the A/D converter.                                                                                                                                               |

| 16      | SCK             | > 2.1 V | Vcc1<br>15 μ Θ<br>200<br>W<br>GND1    | Clock input pin of the serial interface. Refer to "TRUTH TABLE" of pin 19.                                                                                                                   |

| PIN NO. | PIN NAME | VOLTAGE | EQUIVALENT CIRCUIT                    | DESCRIPTION                                                                                                                                                                                                                      |  |  |

|---------|----------|---------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 17      | VCC4     | 5.0 V   |                                       | Analog power supply pin of the A/D converter.                                                                                                                                                                                    |  |  |

| 18      | GND4     | 0.0 V   |                                       | Analog GND pin of the A/D converter.                                                                                                                                                                                             |  |  |

| 19      | SDATA    | > 2.1 V | V <sub>CC1</sub> 15 μ Θ  200  W  GND1 | Data input pin of the serial interface.  TRUTH TABLE  SDATA SCK Action DATA ↑ SHIFT 0 ↓ - 1 ↓ STORE                                                                                                                              |  |  |

| 20      | CLPCAP   | 3.2 V   | Vcc1<br>200<br>100 μ Θ<br>GND1        | Bias decoupling pin of the CDS signal clamp circuit. This pin is connected to the GND1 via a capacitor.                                                                                                                          |  |  |

| 21      | CCDIN    | 2.5 V   | Vcc1<br>26 k ≷ 150 μ ⊗<br>200         | Signal input pin of the CDS. Input CCD signal to this pin via a capacitor.                                                                                                                                                       |  |  |

| 22      | REFIN    | 2.5 V   | <b>A</b> 26 k ≥ 150 μ ⊖ GND1          | Reference input pin of the CDS. This pin is connected to the GND1 via a capacitor.                                                                                                                                               |  |  |

| 23      | GND1     | 0.0 V   |                                       | GND pin of the CDS/AGC. Pay careful attention to board layout of the GND1 because the CDS/AGC are noise-sensitive circuitry.                                                                                                     |  |  |

| 24      | SHISET   | 1.7 V   | 2 k ≥ 2 k ≥ 26 k ≥ 26 k ≥ 13 k ≥ GND1 | Operation current setting pin of the CDS and \$\overline{S}\$/H3 circuits.  This pin is connected to the GND1 via a resistor.  The slew rates of the \$\overline{S}\$/Hs are in inverse proportion to the value of the resistor. |  |  |

| PIN NO. | PIN NAME | VOLTAGE                               | EQUIVALENT CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                 |

|---------|----------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25      | VCC1     | 5.0 V                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Power supply pin of the CDS/AGC.                                                                                                                                            |

| 26      | REFCAP   | 3.2 V                                 | 200<br>63 k ≥ 2 k ≥ 150 µ ⊖ GND1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bias decoupling pin of the CDS reference clamp circuit. This pin is connected to the GND1 via a capacitor.                                                                  |

| 27      | STBY     | 5.0 V<br>(open)<br>> 2.1 V<br>< 0.7 V | Vcc1<br>110 k ₹ 40 µ ⊖ 68 k ₹<br>200<br>W 65 k ₹<br>10 k 32 k ₹<br>75 k ₹                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Standby function control pin. All actions stop and the power consumption is decreased when low. The threshold voltage has 0.4 V hysteresis. Connect to the Vcc if not used. |

| 28      | CLP      |                                       | Vcc1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pulse input pin of the CDS feed-<br>through level clamp.<br>Signal is clamped when low.                                                                                     |

| 29      | S/H1     | > 2.1 V                               | 50 µ 🖯                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pulse input pin of the \$\overline{S}\$/H1. Signal is sampled when low.                                                                                                     |

| 30      | S/H2     |                                       | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pulse input pin of the \$\overline{S}/\text{H}_2.\$ Signal is sampled when low.                                                                                             |

| 31      | SH₃      | < 0.7 V                               | 100 ≶                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pulse input pin of the \$\overline{S}\$/H3. Signal is sampled when low.                                                                                                     |

| 32      | OBP      |                                       | GND <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Pulse input pin of the OPB clamp and bias error amplifier. Signal is clamped when low.                                                                                      |

| 33      | OBCAP    | 3.7 V                                 | 3.3 k ≥ 20 k ≥ 3.3 k | Clamp capacitor pin of the optical black clamp (OPB clamp) circuit. Connect to the GND2 via a capacitor.                                                                    |

| PIN NO. | PIN NAME | VOLTAGE              | EQUIVALENT CIRCUIT                           | DESCRIPTION                                                                                                                               |

|---------|----------|----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 34      | OFSCTL   | 2.15<br>to<br>2.30 V | Vcc1  200 30 k  W  100 μ   2.2 V   D/A  GND1 | Decoupling capacitor pin of the blanking offset control D/A converter. Connect to the GND1 via a capacitor.                               |

| 35      | BLK      | > 2.1 V              | 35 VCC2 20 µ GND2                            | Blanking pulse input pin. The output of the AGCOUT pin is blanked when low. The blanking level can be controlled by the serial interface. |

| 36      | VCC2     | 5.0 V                |                                              | Power supply pin of the $\overline{S}/Hs$ and OPB clamp circuits.                                                                         |

| 37      | GND2     | 0.0 V                |                                              | GND pin of the \$\overline{S}\$/H3 and OPB clamp circuits.                                                                                |

| 38      | Vcc3     | 5.0 V                |                                              | Power supply pin of the output buffer circuit connected to the AGCOUT pin.                                                                |

| 39      | AGCOUT   | 0.9 V<br>(OBP = L)   | Vcc3<br>300 ₹<br>20<br>W 39<br>GND3          | Signal output pin of the AGC. Connect to the ADIN pin via a capacitor.                                                                    |

| 40      | GND3     | 0.0 V                |                                              | GND pin of the output buffer circuit connected to the AGCOUT pin.                                                                         |

| 41      | AGCCTL   | 2.5<br>to<br>3.8 V   | Vcc1  50 µ 9  200  11 k  M  GND1             | Decoupling capacitor pin of the AGC gain control D/A converter. Connect to the GND1 via a capacitor.                                      |

| PIN NO. | PIN NAME | VOLTAGE                                              | EQUIVALENT CIRCUIT                                                 | DESCRIPTION                                                                                                                                                                      |

|---------|----------|------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42      | ADOFS    | 3.3 V<br>(open)<br>Input range<br>1.6<br>to<br>5.0 V | Vcc4<br>70 k<br>70 k<br>70 k<br>79 k<br>79 k<br>75 μ ⊖ 75 μ ⊖ GND4 | Voltage adjustment pin of the ADC black level clamp. This pin is biased at 3.3 V from the inside of the IC. Connect to the GND4 via a capacitor if not used.                     |

| 43      | ADIN     | 1.4 V<br>( <del>ADCLP</del> = L)                     | Vcc4<br>50 µ ⊗<br>50 µ ⊗<br>16 k ₹ 16 k ₹<br>GND4                  | Signal input pin of the ADC. Connect to the AGCOUT pin via a capacitor. This capacitor is also used as the clamp capacitor of the ADC blank level clamp.                         |

| 44      | NC       |                                                      |                                                                    | No connection. It is recommended to connect to GND for better heat radiation and avoiding noise.                                                                                 |

| 45      | ADCLP    | > 2.1 V                                              | 25 µ GND4                                                          | Pulse input pin of the ADC black<br>level clamp. Signal is clamped<br>when low.<br>When the ADOFS is opened, the<br>clamped level is set to make the<br>ADC output 61 (decimal). |

| 46      | VRT      | 3.90 V                                               | VCC4  VCC4  VCC4  VCC4                                             | Upper reference decoupling pin of the ADC. Connect to the GND4 via a capacitor.                                                                                                  |

| 47      | VrB      | 1.95 V                                               | GND4  GND4                                                         | Lower reference decoupling pin of<br>the ADC. Connect to the GND4 via<br>a capacitor.                                                                                            |

| PIN NO. | PIN NAME | VOLTAGE | EQUIVALENT CIRCUIT | DESCRIPTION                                                                                                                                                                          |

|---------|----------|---------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 48      | VLOGIC   | 3.3 V   | 25 µ S GND5        | ADC output voltage setting pin. The high level voltage of the DOo to DO9 pins is set to VLOGIC – 0.2 V. It is recommended to connect to the power supply of the following logic ICs. |

#### **FUNCTIONAL DESCRIPTION**

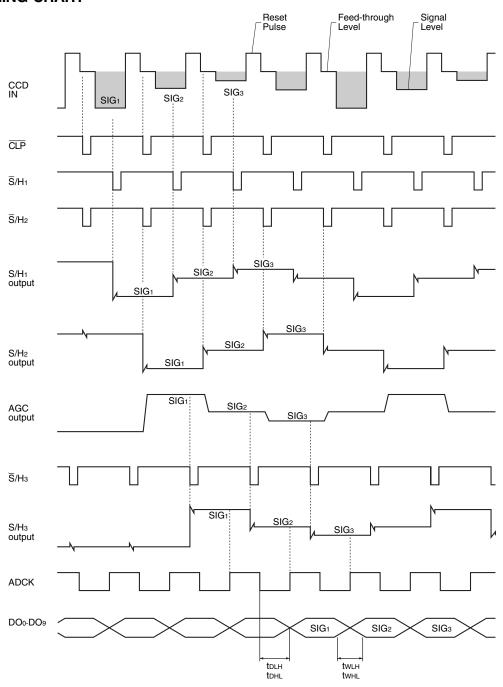

#### **CDS Circuit**

The clamp circuit clamps the feed-through level of the CCD signal with the  $\overline{\text{CLP}}$  pulse. Then the  $\overline{\text{S}}/\text{H}_1$  circuit samples the signal period of the one with the  $\overline{\text{S}}/\text{H}_1$  pulse and holds on. Thus the video signal is obtained. But this signal has a level drop caused by the reset pulse of the CCD signal, and for removing it, the  $\overline{\text{S}}/\text{H}_2$  circuit samples this signal again with the  $\overline{\text{S}}/\text{H}_2$  pulse.

For reducing the effect of the sampling pulse or other noise sources, the CDS circuit is formed with a differential structure.

# **Bias Error Amplifier Circuit**

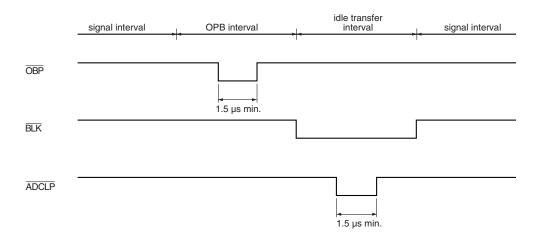

For stabilizing the bias level of the CDS circuit and reducing the offset of the AGC circuit, the bias error amplifier acts with the  $\overline{\text{OBP}}$  pulse during the OPB period.

# **AGC Amplifier Circuit**

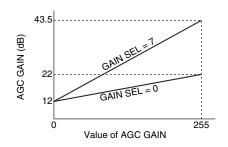

The AGC amplifier amplifies the video signal obtained by the CDS circuit. The gain of the AGC is controlled by the value of the AGCGAIN serial register. And the maximum gain of the AGC is controlled by the value of the GAINSEL serial register.

# **OPB Clamp Circuit**

For clamping the level of the amplified signal to the black level, the OPB clamp circuit acts with the  $\overline{\text{OBP}}$  pulse during the OPB period.

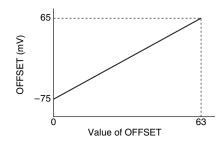

## **Blanking Circuit**

The output signal is fixed to the blanking level with the  $\overline{\text{BLK}}$  pulse. The blanking level is the sum of the black level and the offset value decided by the value of the OFFSET serial register.

#### A/D Converter Circuit

The  $\overline{S}/H3$  circuit samples the amplified signal with the  $\overline{S}/H3$  pulse and the A/D converter converts the sampled signal to 10-bit straight binary digital data. The clamp circuit placed in front of the A/D converter clamps the signal level beside the lower limit of the convertible input range with the  $\overline{ADCLP}$  pulse. The clamped level is controllable by the voltage of the ADOFS pin.

The A/D conversion is executed at the rising edge of the ADCK clock, and the data is output at the falling edge.

The high level voltage of the outputs is controlled by the voltage of the VLogic pin.

# **Standby Function**

By making the STBY pin low, all actions of this IC stop and power consumption is decreased.

The outputs of the A/D converter (DO<sub>0</sub> to DO<sub>9</sub>) turn to high impedance when on standby.

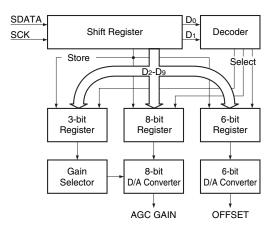

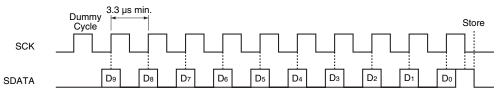

#### **Serial Interface Circuit**

The IR3Y38M has a serial interface to control the gain of the AGC amplifier and the offset of the blanking level. This interface is constituted by a shift register for serial-parallel conversion, data registers and D/A converters.

The data input to SDATA is fetched and shifted at

the rising edge of the SCK. While transmitting data, the SDATA must be low when the SCK falls. When the SDATA is high and the SCK falls, the data on the shift register is stored at the selected data register at the following falling edge of the SDATA. The stored data register is selected by the data of the Do and D1 bits.

| GAIN SEL | MAXIMUM GAIN (dB) |

|----------|-------------------|

| 0        | 22                |

| 1        | 25                |

| 2        | 28                |

| 3        | 31.5              |

| 4        | 34.5              |

| 5        | 38                |

| 6        | 41                |

| 7        | 43.5              |

| DATA REGISTER | D9         | D8 | D7 | D6  | D5 | D4         | Dз | D2         | D1 | Do |

|---------------|------------|----|----|-----|----|------------|----|------------|----|----|

| GAIN SEL      |            |    |    |     |    | do         | d1 | <b>d</b> 2 | 0  | 0  |

| AGC GAIN      | <b>d</b> o | d1 | d2 | dз  | d4 | <b>d</b> 5 | d6 | d7         | 0  | 1  |

| OFFSET        |            |    | do | d1  | d2 | dз         | d4 | <b>d</b> 5 | 1  | 0  |

| (Don't care)  |            |    |    |     |    |            |    |            | 1  | 1  |

| LSB           |            |    |    | MSB |    |            |    |            |    |    |

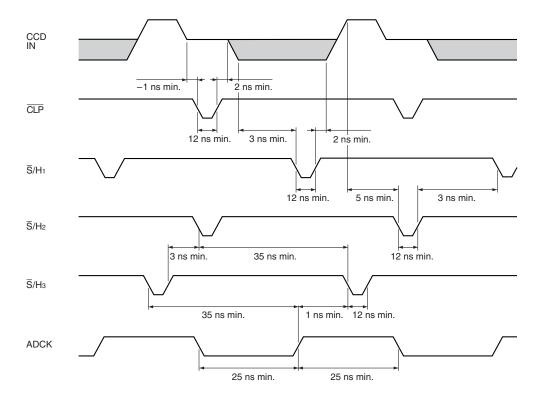

# **TIMING CHART**

#### **PRECAUTIONS**

Each Vcc1 to Vcc6 pin corresponds to the each GND1 to GND6 pin. Connect a ceramic capacitor as near the IC as possible between each corresponding Vcc pin and GND pin.

The GND<sub>1</sub> pin is the ground of the CDS/ADC circuit handling a weak signal. Pay careful attention to the board layout of the GND<sub>1</sub> pattern in order to avoid the potential fluctuation of the GND<sub>1</sub> caused by the current of the other GND pins. Especially pay attention to the current of the GND<sub>6</sub> pin's flowing spiky current.

All the GND pins must be at the same potential and not open. And keep the potential difference of each Vcc pin within 0.3 V.

The high level voltage of the outputs of the A/D

converter is controllable by the voltage of the VLOGIC pin, but take care that the high level voltage does not fall below about 1.5 V, in spite of making the VLOGIC pin 0 V. This may cause the latch up of the following logic ICs if the power supply of this IC rises up faster than the power supply of the following logic. To avoid this problem, it is recommended to make the  $\overline{\text{STBY}}$  pin low until the voltage of the logic power supply becomes stable. Take care too that the high level voltage does not rise above about VCC - 1.0 V, in spite of making the VLOGIC pin the VCC potential.

Restore the value of the serial register when setting up the power supply or making the STBY pin high because the value will have been removed in that case.

#### ABSOLUTE MAXIMUM RATINGS

(Unless otherwise specified, TA = +25 °C)

| PARAMETER             | SYMBOL    | CONDITIONS             | RATING            | UNIT  |

|-----------------------|-----------|------------------------|-------------------|-------|

| Supply voltage        | VCC1-VCC6 |                        | 7                 | V     |

| Input voltage         | VIN       |                        | -0.3 to Vcc + 0.3 | V     |

| Power consumption     | PD        | $TA \le +25 ^{\circ}C$ | 570               | mW    |

| PD derating ratio     |           | Ta > +25 °C            | 4.5               | mW/°C |

| Operating temperature | Topr      |                        | -30 to +70        | °C    |

| Storage temperature   | Tstg      |                        | -55 to +150       | °C    |

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER                        | SYMBOL    | APPLICABLE PINS                                                       | RATING       | UNIT  |  |

|----------------------------------|-----------|-----------------------------------------------------------------------|--------------|-------|--|

| Supply voltage                   | VCC1-VCC6 |                                                                       | 4.75 to 5.25 | V     |  |

| Standard CCD input signal level  | Vccd      | CCDIN                                                                 | 200          | mVp-p |  |

| Input "Low" voltage              | VIL       | ADCK, SCK, SDATA,<br>STBY, CLP, S/H <sub>1</sub> , S/H <sub>2</sub> , | 0 to 0.7     | V     |  |

| Input "High" voltage             | VIH       | S/H <sub>3</sub> , OBP, BLK, ADCLP                                    | 2.1 to Vcc   | V     |  |

| S/H pulse width                  | tws/H     | CLP, S/H1, S/H2, S/H3                                                 | ≥ 12         | ns    |  |

| Clamp pulse width                | twc       | OBP, ADCLP                                                            | ≥ 1.5        | μs    |  |

| A/D converter clock frequency    | fadck     | ADCK                                                                  | ≤ 18         | MHz   |  |

| Serial interface clock frequency | fsck      | SCK                                                                   | ≤ 300        | kHz   |  |

## **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

(Unless otherwise specified, Ta = +25 °C, Vcc1 = Vcc2 = Vcc3 = Vcc4 = Vcc5 = Vcc6 = 5.0 V, VLogIC = 3.3 V, ADCK = 0 V, SCK = 0 V, SDATA = 0 V,  $\overline{STBY}$  = 3.3 V,  $\overline{CLP}$  = 0 V,  $\overline{S}/H_1$  = 0 V,  $\overline{S}/H_2$  = 0 V,  $\overline{S}/H_3$  = 0 V,  $\overline{BLK}$  = 3.3 V,  $\overline{OBP}$  = 0 V, SW42 = OFF, SW43 = (a),  $\overline{ADCLP}$  = 3.3 V)

The current direction flowing into the pin is positive direction.

#### General

| PARAMETER                | SYMBOL      | CONDITIONS                                                                                                                                                                                                                                                       | MIN. | TYP. | MAX. | UNIT |

|--------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply current (1)       | ICC1        | Measure pin 25 (Vcc1)                                                                                                                                                                                                                                            | _    | 27   | 34   | mA   |

| Supply current (2)       | ICC2        | Measure pin 36 (Vcc2).                                                                                                                                                                                                                                           | _    | 2.3  | 2.8  | mA   |

| Supply current (3)       | Іссз        | Measure pin 38 (Vcc3).                                                                                                                                                                                                                                           | _    | 0.7  | 1.0  | mA   |

| Supply current (4)       | ICC4        | Measure pin 17 (Vcc4).                                                                                                                                                                                                                                           | _    | 13   | 20   | mA   |

| Supply current (5)       | ICC5        | Measure pin 15 (VCC5).                                                                                                                                                                                                                                           | _    | 16   | 21   | mA   |

| Supply current (6)       | ICC6        | Measure pin 7 (Vcc6).                                                                                                                                                                                                                                            | _    | 5.0  | 6.5  | mA   |

| Total supply current     | Icc         | Total of lcc1 to lcc6                                                                                                                                                                                                                                            | _    | 63   | 77   | mA   |

| Standby supply current   | ISTBY       | STBY = 0 V, Total of Icc1 to Icc6.                                                                                                                                                                                                                               | _    | 4.5  | 6.5  | mA   |

| Input "Low" current      | IIL1        | Apply to pin 28 ( $\overline{\text{CLP}}$ ), pin 29 ( $\overline{\text{S}}$ /H <sub>1</sub> ), pin 30 ( $\overline{\text{S}}$ /H <sub>2</sub> ), pin 31 ( $\overline{\text{S}}$ /H <sub>3</sub> ), and pin 32 ( $\overline{\text{OBP}}$ ). V <sub>IL</sub> = 0 V | -3.5 | -2.0 | _    | μΑ   |

| Input "High" current     | liH1        | Apply to pin 28 ( $\overline{\text{CLP}}$ ), pin 29 ( $\overline{\text{S}}$ /H <sub>1</sub> ), pin 30 ( $\overline{\text{S}}$ /H <sub>2</sub> ), pin 31 ( $\overline{\text{S}}$ /H <sub>3</sub> ), and pin 32 ( $\overline{\text{OBP}}$ ). VIH = 3.3 V           | _    | 0    | 0.1  | μΑ   |

| Input "Low" current (2)  | lIL2        | Apply to pin 16 (SCK) and pin 19 (SDATA).  VIL = 0 V                                                                                                                                                                                                             | -0.3 | -0.2 | _    | μΑ   |

| Input "High" current (2) | liH2        | Apply to pin 16 (SCK) and pin 19 (SDATA).<br>VIH = 3.3 V                                                                                                                                                                                                         | _    | 0    | 0.1  | μΑ   |

| Input "Low" current (3)  | lıl3        | Apply to pin 35 ( $\overline{BLK}$ ) and pin 45 ( $\overline{ADCLP}$ ). VIL = 0 V                                                                                                                                                                                | -0.5 | -0.3 | 0    | μΑ   |

| Input "High" current (3) | Іінз        | Apply to pin 35 ( $\overline{BLK}$ ) and pin 45 ( $\overline{ADCLP}$ ). ViH = 3.3 V                                                                                                                                                                              | _    | 0    | 0.1  | μΑ   |

| Input "Low" current (4)  | IIL4        | Apply to pin 13 (ADCK). VIL = 0 V                                                                                                                                                                                                                                | -3.5 | -2.0 | _    | μΑ   |

| Input "High" current (4) | liH4        | Apply to pin 13 (ADCK).<br>VIH = 3.3 V                                                                                                                                                                                                                           | _    | 0    | 0.1  | μΑ   |

| STBY voltage             | V27         | Open pin 27 (STBY).                                                                                                                                                                                                                                              | 4.5  | 5.0  | _    | V    |

| STBY impedance           | <b>Z</b> 27 |                                                                                                                                                                                                                                                                  | 70   | 110  | 140  | kΩ   |

## • CDS & AGC Circuits

| PARAMETER        | SYMBOL       | CONDITIONS                     | MIN. | TYP. | MAX. | UNIT |

|------------------|--------------|--------------------------------|------|------|------|------|

| CLPCAP voltage   | V20          |                                | 2.9  | 3.2  | 3.6  | ٧    |

| CCDIN voltage    | V21          |                                | 2.3  | 2.5  | 2.8  | ٧    |

| REFIN voltage    | V22          |                                | 2.3  | 2.5  | 2.8  | ٧    |

| SHISET voltage   | V24          |                                | 1.5  | 1.7  | 1.9  | ٧    |

| REFCAP voltage   | V26          |                                | 2.9  | 3.2  | 3.6  | ٧    |

| OBCAP voltage    | V33          |                                | 3.3  | 3.7  | 4.0  | ٧    |

| AGCOUT voltage   | <b>V</b> 39  |                                | 0.7  | 0.9  | 1.1  | ٧    |

| CCDIN impedance  | <b>Z</b> 21  |                                | 9    | 13   | 18   | kΩ   |

| REFIN impedance  | <b>Z</b> 22  |                                | 9    | 13   | 18   | kΩ   |

| REFCAP impedance | <b>Z</b> 26  |                                | 15   | 23   | 32   | kΩ   |

| OFSCTL impedance | <b>Z</b> 34  |                                | 6    | 9    | 12   | kΩ   |

| AGCCTL impedance | <b>Z</b> 41  |                                | 7    | 11   | 15   | kΩ   |

| CLPCAP charge    | IL20         | CLPCAP = 2.8 V, OBP = 0 V      |      | -135 | 110  |      |

| current          | IL20         | Measure the current of CLPCAP. | _    | -135 | -110 | μA   |

| CLPCAP discharge | IH20         | CLPCAP = 3.6 V, OBP = 0 V      | 110  | 135  |      |      |

| current          | IH20         | Measure the current of CLPCAP. | 110  | 135  | _    | μΑ   |

| CLPCAP leakage   | <b>I</b> Z20 | CLPCAP = 3.2 V, OBP = 3.3 V    | -0.5 | 0    | 0.5  |      |

| current          | 1220         | Measure the current of CLPCAP. | -0.5 |      | 0.5  | μΑ   |

| OBCAP charge     | IL33         | OBCAP = 3.3 V, OBP = 0 V       |      | -90  | CE   |      |

| current          | IL33         | Measure the current of OBCAP.  | _    | -90  | -65  | μΑ   |

| OBCAP discharge  | lugo         | OBCAP = 4.1 V, OBP = 0 V       | C.F. | 00   |      |      |

| current          | Інзз         | Measure the current of OBCAP.  | 65   | 90   | _    | μΑ   |

| OBCAP leakage    | 1700         | OBCAP = 3.7 V, OBP = 3.3 V     | 0.5  | 0    | 0.5  |      |

| current          | IZ33         | Measure the current of OBCAP.  | -0.5 | U    | 0.5  | μΑ   |

## • A/D Converter Circuit

| PARAMETER             | SYMBOL      | CONDITIONS                               | MIN. | TYP. | MAX. | UNIT |

|-----------------------|-------------|------------------------------------------|------|------|------|------|

| ADOFS voltage         | V42         |                                          | 3.0  | 3.3  | 3.6  | V    |

| ADIN voltage          | V43         | ADCLP = 0 V                              | 1.2  | 1.4  | 1.6  | V    |

| VRT voltage           | <b>V</b> 46 |                                          | 3.7  | 3.9  | 4.1  | V    |

| VRB voltage           | <b>V</b> 47 |                                          | 1.8  | 1.95 | 2.2  | V    |

| ADOFS impedance       | <b>Z</b> 42 |                                          | 50   | 70   | 90   | kΩ   |

| ADIN shows a surrent  | IL43        | ADIN = 1.0 V, ADCLP = 0 V                | _    | -45  | -30  | μА   |

| ADIN charge current   |             | Measure the current of ADIN.             |      |      |      |      |

| ADIN discharge        | IH43        | ADIN = 1.8 V, ADCLP = 0 V                | 30   | 45   | _    | μА   |

| current               | IH43        | Measure the current of ADIN.             |      |      |      |      |

| ADIN lookogo ourront  | <br> Z43    | ADIN = 1.4 V, ADCLP = 3.3 V              | -0.3 | 0    | 0.3  | μА   |

| ADIN leakage current  | 1243        | Measure the current of ADIN.             |      |      |      |      |

|                       | VoL         | SW43 = (b), ADCIN = 0.8 V                |      |      |      |      |

| Output "Low" voltage  |             | Change the level of ADCK to L→H→L, then  | _    | 0.2  | 0.4  | V    |

|                       |             | measure the voltages of DOo to DO9 pins. |      |      |      |      |

| Output "High" voltage | Vон         | SW43 = (b), ADCIN = 3.5 V                | 2.9  | 3.1  | _    | V    |

|                       |             | Change the level of ADCK to L→H→L, then  |      |      |      |      |

|                       |             | measure the voltages of DOo to DO9 pins. |      |      |      |      |

## **AC Characteristics**

(Unless otherwise specified, TA = +25 °C, Vcc1 = Vcc2 = Vcc3 = Vcc4 = Vcc5 = Vcc6 = 5.0 V, VLogic = 3.3 V, ADCK = 0 V, SCK = 0 V, SDATA = 0 V,  $\overline{STBY}$  = 3.3 V,  $\overline{CLP}$  = 3.3 V,  $\overline{S}/H_1$  = 0 V,  $\overline{S}/H_2$  = 0 V,  $\overline{S}/H_3$  = 0 V,  $\overline{BLK}$  = 3.3 V,  $\overline{OBP}$  = 3.3 V, SW42 = OFF, SW43 = (a),  $\overline{ADCLP}$  = 3.3 V, (OFFSET) = 32) The value of the serial register is written with decimal.

#### • CDS & AGC Circuits

| PARAMETER               | SYMBOL            | CONDITIONS                                                                                                 | MIN. | TYP. | MAX. | UNIT |

|-------------------------|-------------------|------------------------------------------------------------------------------------------------------------|------|------|------|------|

| AGC minimum gain        | Gan               | (GAIN SEL) = 0, $(AGC GAIN) = 0\overline{CLP} = SG2, \overline{OBP} = SG3$                                 | 11   | 12   | 13   | dB   |

|                         |                   | Input the attenuated SG1 (f = 2 MHz, V = 1.6 Vp-p) to the SIN and seek the attenuation                     |      |      |      |      |

|                         |                   | amount to make the amplitude of AGCOUT 1.6 Vp-p.                                                           |      |      |      |      |

| AGC maximum gain (0)    | GAX0              | (GAIN SEL) = 0, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 20.5 | 22   | 24.5 | dB   |

| AGC maximum gain        | GAX1              | (GAIN SEL) = 1, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 23   | 25   | 28   | dB   |

| AGC maximum gain (2)    | GAX2              | (GAIN SEL) = 2, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 26   | 28   | 31   | dB   |

| AGC maximum gain        | G <sub>A</sub> хз | (GAIN SEL) = 3, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 28.5 | 31.5 | 35   | dB   |

| AGC maximum gain (4)    | GAX4              | (GAIN SEL) = 4, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 31   | 34.5 | 38   | dB   |

| AGC maximum gain (5)    | GAX5              | (GAIN SEL) = 5, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 34   | 38   | 42   | dB   |

| AGC maximum gain (6)    | GAX6              | (GAIN SEL) = 6, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 36.5 | 41   | 44.5 | dB   |

| AGC maximum gain (7)    | Gax7              | (GAIN SEL) = 7, (AGC GAIN) = 255  Measure the gain using the same procedure as for the measurement of GAN. | 38.5 | 43.5 | 47.5 | dB   |

| AGC gain variable width | GAR               | GAR = GAX7 – GAN                                                                                           | 26.5 | 31.5 | 35.5 | dB   |

| PARAMETER                                     | SYMBOL | CONDITIONS                                                                                                                                                                                                                                                                                   | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Bandwidth (1)<br>(Minimum gain)               | fтn    | (GAIN SEL) = 0, (AGC GAIN) = 0 $\overline{\text{CLP}} = \text{SG2}, \overline{\text{OBP}} = \text{SG3}$ Input the SG1 (f = 2 MHz, V = 0.2 Vp-p) to the SIN and measure the amplitude of the AGCOUT. Increase the frequency and measure the frequency when the amplitude attenuates to -3 dB. | 24   | 35   | Т    | MHz  |

| Bandwidth (2)<br>(Maximum gain)               | fтх    | (GAIN SEL) = 7, (AGC GAIN) = 255  CLP = SG2, OBP = SG3 Input the SG1 (f = 2 MHz, V = 8 mVp-p) to the SIN and measure the amplitude of the AGCOUT. Increase the frequency and measure the frequency when the amplitude attenuates to -3 dB.                                                   | 13   | 20   | -    | MHz  |

| OFFSET adjustment limit (1) (OFFSET = 0)      | VBON   | (GAIN SEL) = 0, (AGC GAIN) = 0  SIN = GND1, (OFFSET) = 0, $\overline{\text{CLP}}$ = 0 V, $\overline{\text{OBP}}$ = 0 V  Measure the voltage of the AGCOUT at BLK = 3.3 V and define it VB011.  Measure the one similarly at BLK = 0 V and define it VB012.  VBON = VB012 - VB011             | -    | -75  | -60  | mV   |

| OFFSET adjustment limit (2) (OFFSET = 63)     | Vвох   | (GAIN SEL) = 0, (AGC GAIN) = 0 SIN = GND1, (OFFSET) = 63, $\overline{\text{CLP}}$ = 0 V, $\overline{\text{OBP}}$ = 0 V Measure the VB021 and VB022 similarly to above-mentioned method. VB0N = VB022 - VB021                                                                                 | 50   | 65   | -    | mV   |

| Output dynamic<br>range (1)<br>(Minimum gain) | Vdyn   | (GAIN SEL) = 0, (AGC GAIN) = 0 $\overline{\text{CLP}} = \text{SG2}, \overline{\text{OBP}} = \text{SG3}$ Input the SG1 (f = 2 MHz, V = 0.9 Vp-p) to the SIN and measure the amplitude of the AGCOUT.                                                                                          | 2.0  | 2.2  | -    | Vp-p |

| Output dynamic<br>range (2)<br>(Maximum gain) | VDYX   | $\begin{aligned} &(\text{GAIN SEL}) = 7,  (\text{AGC GAIN}) = 255\\ &\overline{\text{CLP}} = \text{SG2},  \overline{\text{OBP}} = \text{SG3}\\ &\text{Input the SG1 (f = 2 MHz, V = 50 mVp-p) to the}\\ &\text{SIN and measure the amplitude of the AGCOUT.} \end{aligned}$                  | 2.0  | 2.2  | -    | Vp-p |

#### A/D Converter Circuit

(Unless otherwise specified, TA = +25 °C, VCC1 = VCC2 = VCC3 = VCC4 = VCC5 = VCC6 = 5.0 V, VLOGIC = 3.3 V, ADCK = 18 MHz square wave,  $\overline{SCK}$ = 0 V,  $\overline{SDATA}$  = 0 V,  $\overline{STBY}$  = 3.3 V,  $\overline{CLP}$  = 3.3 V,  $\overline{S}/H_1$  = 0 V,  $\overline{S}/H_2$  = 0 V,  $\overline{S}/H_3$  = 0 V,  $\overline{BLK}$  = 3.3 V,  $\overline{OBP}$  = 3.3 V, SW42 = OFF, SW43 = (b),  $\overline{ADCLP}$  = 3.3 V)

| PARAMETER                | SYMBOL | CONDITIONS                                                    | MIN. | TYP. | MAX. | UNIT |

|--------------------------|--------|---------------------------------------------------------------|------|------|------|------|

|                          | DCLP   | SW43 = (a)                                                    | 56   | 61   | 66   | -    |

| Clamp value              |        | ADCLP = 0 V                                                   |      |      |      |      |

| Clamp value              |        | ADCIN = GND4                                                  |      |      |      |      |

|                          |        | Read the output value of DO <sub>0</sub> to DO <sub>9</sub> . |      |      |      |      |

| Clamp value              | DCLPN  | SW42 = ON, V42 = 5.0 V, ADCLP = 0 V,                          |      |      |      |      |

| adjustment limit (1)     |        | ADCIN = GND4                                                  | 31   | 36   | 41   | -    |

| aujustinent iiniit (1)   |        | Read the output value of DO <sub>0</sub> to DO <sub>9</sub> . |      |      |      |      |

| Clamp value              |        | SW42 = ON, V42 = 1.6 V, ADCLP = 0 V,                          |      |      |      |      |

| adjustment limit (2)     | DCLPX  | ADCIN = GND4                                                  | 81   | 86   | 91   | -    |

| aujustinent iiniit (2)   |        | Read the output value of DO <sub>0</sub> to DO <sub>9</sub> . |      |      |      |      |

| Differential linearity   |        | ADCIN = SG4                                                   |      | ±0.5 | ±0.9 | LSB  |

| error                    | DLE    | Read the output value of DOo to DOo at about                  | _    |      |      |      |

|                          | ILE    | 106 times and make it a histogram. Normalize                  |      |      |      |      |

| Integral linearity error |        | the histogram and obtain the DLE.                             | _    | ±3   | ±7   | LSB  |

| ,                        |        | Integrate the histogram and obtain the ILE.                   |      |      |      |      |

|                          | tDLH   | ADCIN = SG4, CL = 20 pF                                       | 15   | 26   | 38   | ns   |

| Propagation delay        |        | Measure the delay time from the falling edge                  |      |      |      |      |

| (L→H)                    |        | (50%) of the ADCK to the rising edge (50%)                    |      |      |      |      |

|                          |        | of the DOo to DO9.                                            |      |      |      |      |

|                          | tDHL   | ADCIN = SG4, CL = 20 pF                                       |      |      |      |      |

| Propagation delay        |        | Measure the delay time from the falling edge                  | 15   | 26   | 38   | ns   |

| (H→L)                    |        | (50%) of the ADCK to the falling edge (50%)                   |      |      |      |      |

|                          |        | of the DOo to DO9.                                            |      |      |      |      |

| Output rise time         | twLH   | ADCIN = SG4, CL = 20 pF                                       |      |      |      |      |

|                          |        | Measure the rise time (10%→90%) of the                        | 10   | 17   | 25   | ns   |

|                          |        | DOo to DO9.                                                   |      |      |      |      |

|                          | twnL   | ADCIN = SG4, CL = 20 pF                                       |      |      |      |      |

| Output fall time         |        | Measure the fall time (90%→10%) of the                        | 10   | 17   | 25   | ns   |

|                          |        | DOo to DO9.                                                   |      |      |      |      |

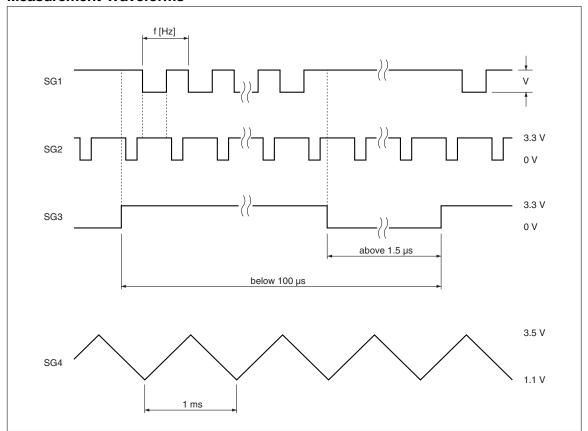

# **Measurement Waveforms**

# **Test Circuit**

PACKAGE (Unit: mm)